Simulation und Vorhersage elektrostatischer Entladungen (ESD) für RF-Bauteile

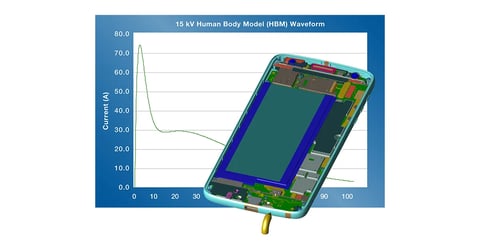

Prüfung der elektrostatischen Entladung (ESD) wird weltweit von Elektronikherstellern verwendet und umfasst die Anwendung zahlreicher Normen von Organisationen wie dem American National Standards Institute (ANSI), JEDEC und der International Electrotechnical Commission (IEC), um nur einige zu nennen. ESD-Tests erfordern den Einsatz vieler Hardware-Prototypen, was zeitaufwendig und teuer ist. Die Möglichkeit, den ESD-Testprozess zu simulieren und die Stellen in drahtlosen Geräten zu identifizieren, die für ESD-Schäden anfällig sind, wäre äußerst wertvoll und würde es den Ingenieuren ermöglichen, die Anzahl der Prototypen zu reduzieren, die für die Entwicklung von Produkten für minimale ESD-Schäden erforderlich sind.

Prüfung der elektrostatischen Entladung (ESD) wird weltweit von Elektronikherstellern verwendet und umfasst die Anwendung zahlreicher Normen von Organisationen wie dem American National Standards Institute (ANSI), JEDEC und der International Electrotechnical Commission (IEC), um nur einige zu nennen. ESD-Tests erfordern den Einsatz vieler Hardware-Prototypen, was zeitaufwendig und teuer ist. Die Möglichkeit, den ESD-Testprozess zu simulieren und die Stellen in drahtlosen Geräten zu identifizieren, die für ESD-Schäden anfällig sind, wäre äußerst wertvoll und würde es den Ingenieuren ermöglichen, die Anzahl der Prototypen zu reduzieren, die für die Entwicklung von Produkten für minimale ESD-Schäden erforderlich sind.

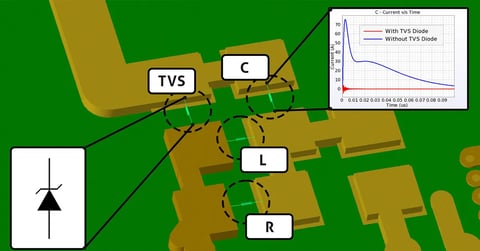

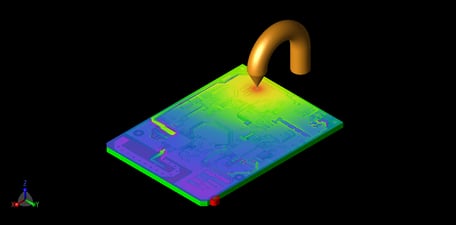

In dieser Präsentation wird eine neue, auf Multiphysik basierende ESD-Analysefunktion vorgestellt, mit der der ESD-Prüfprozess mittels Computersimulation analysiert werden kann. Dies spart Unternehmen Zeit und Geld, da der ESD-Schutz bereits in der Entwurfsphase optimiert werden kann, wodurch die Anzahl der zu bauenden und zu prüfenden Prototypen verringert wird.